- •Features

- •1. Pin Configurations

- •1.1 Disclaimer

- •2. Overview

- •2.1 Block Diagram

- •2.2 Pin Descriptions

- •2.2.3 Port B (PB5..PB0)

- •2.2.4 RESET

- •3. About Code Examples

- •4. AVR CPU Core

- •4.1 Introduction

- •4.2 Architectural Overview

- •4.4 Status Register

- •4.5 General Purpose Register File

- •4.6 Stack Pointer

- •4.7 Instruction Execution Timing

- •4.8 Reset and Interrupt Handling

- •4.8.1 Interrupt Response Time

- •5. AVR ATtiny25/45/85 Memories

- •5.2 SRAM Data Memory

- •5.2.1 Data Memory Access Times

- •5.3 EEPROM Data Memory

- •5.3.1 EEPROM Read/Write Access

- •5.3.5 Atomic Byte Programming

- •5.3.6 Split Byte Programming

- •5.3.7 Erase

- •5.3.8 Write

- •5.3.9 Preventing EEPROM Corruption

- •5.4 I/O Memory

- •6. System Clock and Clock Options

- •6.1 Clock Systems and their Distribution

- •6.2 Clock Sources

- •6.3 Default Clock Source

- •6.4 Crystal Oscillator

- •6.6 Calibrated Internal RC Oscillator

- •6.7 External Clock

- •6.8 128 kHz Internal Oscillator

- •6.9 Clock Output Buffer

- •6.10 System Clock Prescaler

- •6.10.2 Switching Time

- •7. Power Management and Sleep Modes

- •7.1 Idle Mode

- •7.2 ADC Noise Reduction Mode

- •7.4 Power Reduction Register

- •7.5 Minimizing Power Consumption

- •7.5.1 Analog to Digital Converter

- •7.5.2 Analog Comparator

- •7.5.4 Internal Voltage Reference

- •7.5.5 Watchdog Timer

- •7.5.6 Port Pins

- •8. System Control and Reset

- •8.0.1 Resetting the AVR

- •8.0.2 Reset Sources

- •8.0.3 Power-on Reset

- •8.0.4 External Reset

- •8.0.6 Watchdog Reset

- •8.1 Internal Voltage Reference

- •8.2 Watchdog Timer

- •8.3 Timed Sequences for Changing the Configuration of the Watchdog Timer

- •8.3.1 Safety Level 1

- •8.3.2 Safety Level 2

- •9. Interrupts

- •9.1 Interrupt Vectors in ATtiny25/45/85

- •10. External Interrupts

- •11. I/O Ports

- •11.1 Introduction

- •11.2 Ports as General Digital I/O

- •11.2.1 Configuring the Pin

- •11.2.2 Toggling the Pin

- •11.2.3 Switching Between Input and Output

- •11.2.4 Reading the Pin Value

- •11.2.5 Digital Input Enable and Sleep Modes

- •11.2.6 Unconnected Pins

- •11.3 Alternate Port Functions

- •11.3.2 Alternate Functions of Port B

- •12. 8-bit Timer/Counter0 with PWM

- •12.1 Overview

- •12.1.1 Registers

- •12.1.2 Definitions

- •12.2 Timer/Counter Clock Sources

- •12.3 Counter Unit

- •12.4 Output Compare Unit

- •12.4.1 Force Output Compare

- •12.4.2 Compare Match Blocking by TCNT0 Write

- •12.4.3 Using the Output Compare Unit

- •12.5 Compare Match Output Unit

- •12.5.1 Compare Output Mode and Waveform Generation

- •12.6 Modes of Operation

- •12.6.1 Normal Mode

- •12.6.2 Clear Timer on Compare Match (CTC) Mode

- •12.6.3 Fast PWM Mode

- •12.6.4 Phase Correct PWM Mode

- •12.7 Timer/Counter Timing Diagrams

- •13. Timer/Counter Prescaler

- •13.0.1 Prescaler Reset

- •13.0.2 External Clock Source

- •14. 8-bit Timer/Counter1

- •14.1 Timer/Counter1

- •14.1.1 Timer/Counter1 Control Register - TCCR1

- •14.1.2 General Timer/Counter1 Control Register - GTCCR

- •14.1.3 Timer/Counter1 - TCNT1

- •14.1.4 Timer/Counter1 Output Compare RegisterA - OCR1A

- •14.1.5 Timer/Counter1 Output Compare RegisterB - OCR1B

- •14.1.6 Timer/Counter1 Output Compare RegisterC - OCR1C

- •14.1.7 Timer/Counter Interrupt Mask Register - TIMSK

- •14.1.8 Timer/Counter Interrupt Flag Register - TIFR

- •14.1.9 PLL Control and Status Register - PLLCSR

- •14.1.10 Timer/Counter1 Initialization for Asynchronous Mode

- •14.1.11 Timer/Counter1 in PWM Mode

- •15. 8-bit Timer/Counter1 in ATtiny15 Mode

- •15.1 Timer/Counter1 Prescaler

- •15.2 Timer/Counter1

- •15.2.1 Timer/Counter1 Control Register - TCCR1

- •15.2.2 General Timer/Counter1 Control Register - GTCCR

- •15.2.3 Timer/Counter1 - TCNT1

- •15.2.4 Timer/Counter1 Output Compare RegisterA - OCR1A

- •15.2.5 Timer/Counter1 Output Compare Register C - OCR1C

- •15.2.6 Timer/Counter1 Interrupt Mask Register - TIMSK

- •15.2.7 Timer/Counter Interrupt Flag Register - TIFR

- •15.2.8 PLL Control and Status Register - PLLCSR

- •15.2.9 Timer/Counter1 in PWM Mode

- •16. Dead Time Generator

- •16.0.1 Timer/Counter1 Dead Time Prescaler register 1 - DTPS1

- •16.0.2 Timer/Counter1 Dead Time A - DT1A

- •16.0.3 Timer/Counter1 Dead Time B - DT1B

- •17.1 Overview

- •17.2 Functional Descriptions

- •17.2.2 SPI Master Operation Example

- •17.2.3 SPI Slave Operation Example

- •17.2.5 Start Condition Detector

- •17.3 Alternative USI Usage

- •17.3.4 Edge Triggered External Interrupt

- •17.3.5 Software Interrupt

- •17.4 USI Register Descriptions

- •18. Analog Comparator

- •18.1 Analog Comparator Multiplexed Input

- •19. Analog to Digital Converter

- •19.1 Features

- •19.2 Operation

- •19.3 Starting a Conversion

- •19.4 Prescaling and Conversion Timing

- •19.5 Changing Channel or Reference Selection

- •19.5.1 ADC Input Channels

- •19.5.2 ADC Voltage Reference

- •19.6 ADC Noise Canceler

- •19.6.1 Analog Input Circuitry

- •19.6.2 Analog Noise Canceling Techniques

- •19.6.3 ADC Accuracy Definitions

- •19.7 ADC Conversion Result

- •19.7.1 Single Ended Conversion

- •19.7.2 Unipolar Differential Conversion

- •19.7.3 Bipolar Differential Conversion

- •19.7.4 Temperature Measurement (Preliminary description)

- •19.7.7.1 ADLAR = 0

- •19.7.7.2 ADLAR = 1

- •20. debugWIRE On-chip Debug System

- •20.1 Features

- •20.2 Overview

- •20.3 Physical Interface

- •20.4 Software Break Points

- •20.5 Limitations of debugWIRE

- •20.6 debugWIRE Related Register in I/O Memory

- •21. Self-Programming the Flash

- •21.0.1 Performing Page Erase by SPM

- •21.0.2 Filling the Temporary Buffer (Page Loading)

- •21.0.3 Performing a Page Write

- •21.1.2 EEPROM Write Prevents Writing to SPMCSR

- •21.1.3 Reading the Fuse and Lock Bits from Software

- •21.1.4 Preventing Flash Corruption

- •21.1.5 Programming Time for Flash when Using SPM

- •22. Memory Programming

- •22.1 Program And Data Memory Lock Bits

- •22.2 Fuse Bytes

- •22.2.1 Latching of Fuses

- •22.3 Signature Bytes

- •22.3.1 ATtiny25 Signature Bytes

- •22.3.2 ATtiny45 Signature Bytes

- •22.3.3 ATtiny85 Signature Bytes

- •22.4 Calibration Byte

- •22.5 Page Size

- •22.6 Serial Downloading

- •22.6.1 Serial Programming Algorithm

- •22.6.2 Serial Programming Characteristics

- •22.7 High-voltage Serial Programming

- •22.8.2 Considerations for Efficient Programming

- •22.8.3 Chip Erase

- •22.8.4 Programming the Flash

- •22.8.5 Programming the EEPROM

- •22.8.6 Reading the Flash

- •22.8.7 Reading the EEPROM

- •22.8.8 Programming and Reading the Fuse and Lock Bits

- •22.8.9 Reading the Signature Bytes and Calibration Byte

- •23. Electrical Characteristics

- •23.1 Absolute Maximum Ratings*

- •23.2 External Clock Drive Waveforms

- •23.3 External Clock Drive

- •25. Register Summary

- •26. Instruction Set Summary

- •27. Ordering Information

- •27.1 ATtiny25

- •27.2 ATtiny45

- •27.3 ATtiny85

- •28. Packaging Information

- •29. Errata

- •29.1 ATtiny25/45/85 Rev. A

- •30. Datasheet Revision History

- •Table of Contents

23. Electrical Characteristics

23.1Absolute Maximum Ratings*

..................................Operating Temperature |

|

|

|

|

-55°C to +125°C |

|

*NOTICE: |

Stresses beyond those listed under “Absolute |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Maximum Ratings” may cause permanent dam- |

|||

Storage Temperature ..................................... |

|

|

|

|

-65°C to +150°C |

|

|

age to the device. This is a stress rating only and |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

functional operation of the device at these or |

|||

Voltage on any Pin except |

RESET |

|

|

|

|

|

|

|

|

|

|

|

other conditions beyond those indicated in the |

||||||

with respect to Ground ................................ |

|

|

|

-0.5V to VCC+0.5V |

|

|

operational sections of this specification is not |

||||||||||||

Voltage on |

|

with respect to Ground |

-0.5V to +13.0V |

|

|

implied. Exposure to absolute maximum rating |

|||||||||||||

RESET |

|

|

conditions for extended periods may affect |

||||||||||||||||

Maximum Operating Voltage |

|

|

|

|

|

|

|

6.0V |

|

|

device reliability. |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

DC Current per I/O Pin ............................................... |

|

|

|

|

|

|

|

40.0 mA |

|

|

|

|

|

|

|||||

DC Current VCC and GND Pins................................ |

|

|

|

|

|

|

200.0 mA |

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

DC Characteristics T = -40°C to 85°C, V |

CC |

= 1.8V to 5.5V (unless otherwise noted)(1) |

|

|

|||||||||||||||

|

|

|

|

A |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Symbol |

|

Parameter |

|

|

Condition |

|

|

Min. |

|

Typ. |

Max. |

Units |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

VIL |

|

Input Low-voltage |

|

|

Except XTAL1 and |

-0.5 |

|

|

0.2VCC |

V |

|||||||||

|

|

|

|

pin |

|

|

|

|

|||||||||||

|

|

RESET |

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

Except XTAL1 and |

(3) |

|

|

|

|

||||||

VIH |

|

Input High-voltage |

|

|

|

pin |

|

|

0.6VCC |

|

|

VCC +0.5 |

V |

||||||

|

|

RESET |

|

|

|

|

|||||||||||||

VIL1 |

|

Input Low-voltage |

|

|

XTAL1 pin, External |

-0.5 |

|

|

0.1VCC |

V |

|||||||||

|

|

|

Clock Selected |

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

VIH1 |

|

Input High-voltage |

|

|

XTAL1 pin, External |

(3) |

|

|

VCC +0.5 |

V |

|||||||||

|

|

|

Clock Selected |

0.8VCC |

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

VIL2 |

|

Input Low-voltage |

|

|

|

|

|

pin |

|

|

-0.5 |

|

|

0.2VCC |

V |

||||

RESET |

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(3) |

|

|

|

|

VIH2 |

|

Input High-voltage |

RESET pin |

|

|

|

|

VCC +0.5 |

V |

||||||||||

|

|

|

0.9VCC |

|

|

||||||||||||||

VIL3 |

|

Input Low-voltage |

|

|

|

|

|

pin as I/O |

-0.5 |

|

|

0.2VCC |

V |

||||||

|

RESET |

|

|

||||||||||||||||

VIH3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(3) |

|

|

|

|

|

Input High-voltage |

RESET pin as I/O |

|

|

VCC +0.5 |

V |

|||||||||||||

|

0.6VCC |

|

|

||||||||||||||||

|

|

Output Low Voltage(4) |

|

|

I |

OL |

= 10 mA, V = 5V |

|

|

|

0.6 |

V |

|||||||

VOL |

|

|

|

|

|

|

|

|

|

|

|

CC |

|

|

|

|

|

||

|

(Port B) |

|

|

IOL = 5 mA, VCC = 3V |

|

|

|

0.5 |

V |

||||||||||

|

|

|

|

|

|

|

|||||||||||||

VOH |

|

Output High-voltage(5) |

|

|

IOH = -10 mA, VCC = 5V |

4.3 |

|

|

|

V |

|||||||||

|

(Port B) |

|

|

IOH = -5 mA, VCC = 3V |

2.5 |

|

|

|

V |

||||||||||

|

|

|

|

|

|

|

|||||||||||||

IIL |

|

Input Leakage |

|

|

Vcc = 5.5V, pin low |

|

|

|

1 |

µA |

|||||||||

|

Current I/O Pin |

|

|

(absolute value) |

|

|

|

||||||||||||

IIH |

|

Input Leakage |

|

|

Vcc = 5.5V, pin high |

|

|

|

1 |

µA |

|||||||||

|

Current I/O Pin |

|

|

(absolute value) |

|

|

|

||||||||||||

RRST |

|

Reset Pull-up Resistor |

|

|

|

|

|

|

|

|

|

30 |

|

|

60 |

kΩ |

|||

Rpu |

|

I/O Pin Pull-up Resistor |

|

|

|

|

|

|

|

|

|

20 |

|

|

50 |

kΩ |

|||

166 ATtiny25/45/85

2586A–AVR–02/05

ATtiny25/45/85

ATtiny25/45/85

DC Characteristics T |

= -40°C to 85°C, V |

CC |

= 1.8V to 5.5V (unless otherwise noted)(1) |

(Continued) |

|

||||

|

A |

|

|

|

|

|

|

|

|

Symbol |

Parameter |

|

Condition |

|

Min. |

Typ. |

Max. |

Units |

|

|

|

|

|

|

|

|

|

||

|

|

|

Active 1MHz, VCC = 2V |

|

|

0.5 |

mA |

||

|

|

|

Active 4MHz, VCC = 3V |

|

|

4 |

mA |

||

|

Power Supply Current |

Active 8MHz, VCC = 5V |

|

|

10 |

mA |

|||

ICC |

Idle 1MHz, VCC = 2V |

|

|

0.5 |

mA |

||||

|

|

|

|

||||||

|

|

Idle 4MHz, VCC = 3V |

|

|

1.5 |

mA |

|||

|

|

|

|

|

|||||

|

|

|

Idle 8MHz, VCC = 5V |

|

|

5 |

mA |

||

|

Power-down mode |

WDT enabled, VCC = 3V |

|

|

15 |

µA |

|||

|

WDT disabled, VCC = 3V |

|

|

2 |

µA |

||||

|

|

|

|

|

|||||

Notes: 1. All DC Characteristics contained in this data sheet are based on simulation and characterization of other AVR microcontrollers manufactured in the same process technology. These values are preliminary values representing design targets, and will be updated after characterization of actual silicon.

2.“Max” means the highest value where the pin is guaranteed to be read as low.

3.“Min” means the lowest value where the pin is guaranteed to be read as high.

4.Although each I/O port can sink more than the test conditions (10 mA at VCC = 5V, 5 mA at VCC = 3V) under steady state conditions (non-transient), the following must be observed:

1] The sum of all IOL, for all ports, should not exceed 60 mA.

If IOL exceeds the test condition, VOL may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test condition.

5.Although each I/O port can source more than the test conditions (10 mA at VCC = 5V, 5 mA at VCC = 3V) under steady state conditions (non-transient), the following must be observed:

1] The sum of all IOH, for all ports, should not exceed 60 mA.

If IOH exceeds the test condition, VOH may exceed the related specification. Pins are not guaranteed to source current greater than the listed test condition.

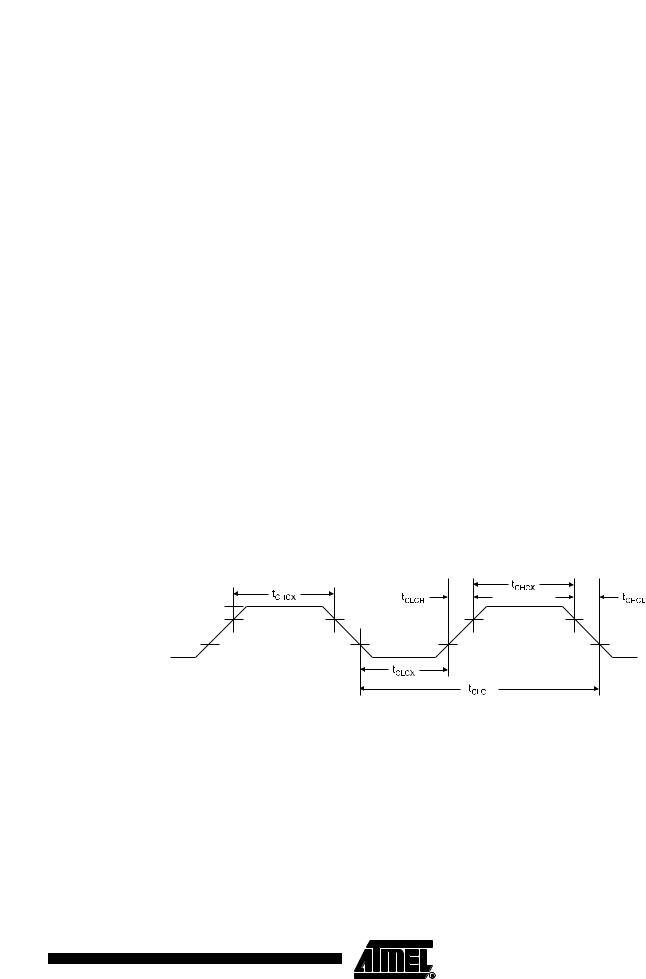

23.2External Clock Drive Waveforms

Figure 23-1. External Clock Drive Waveforms

VIH1

VIL1

0np

167

2586A–AVR–02/05

23.3External Clock Drive

Table 23-1. |

External Clock Drive |

|

|

|

|

|

|

|

|

|

|

|

VCC = 1.8 - 5.5V |

VCC = 2.7 - 5.5V |

VCC = 4.5 - 5.5V |

|

|||

Symbol |

|

Parameter |

Min. |

Max. |

Min. |

Max. |

Min. |

Max. |

Units |

|

|

|

|

|

|

|

|

|

|

1/tCLCL |

|

Clock Frequency |

0 |

4 |

0 |

10 |

0 |

20 |

MHz |

tCLCL |

|

Clock Period |

250 |

|

100 |

|

50 |

|

ns |

tCHCX |

|

High Time |

100 |

|

40 |

|

20 |

|

ns |

tCLCX |

|

Low Time |

100 |

|

40 |

|

20 |

|

ns |

tCLCH |

|

Rise Time |

|

2.0 |

|

1.6 |

|

0.5 |

µs |

tCHCL |

|

Fall Time |

|

2.0 |

|

1.6 |

|

0.5 |

µs |

∆tCLCL |

|

Change in period from one clock cycle to the next |

|

2 |

|

2 |

|

2 |

% |

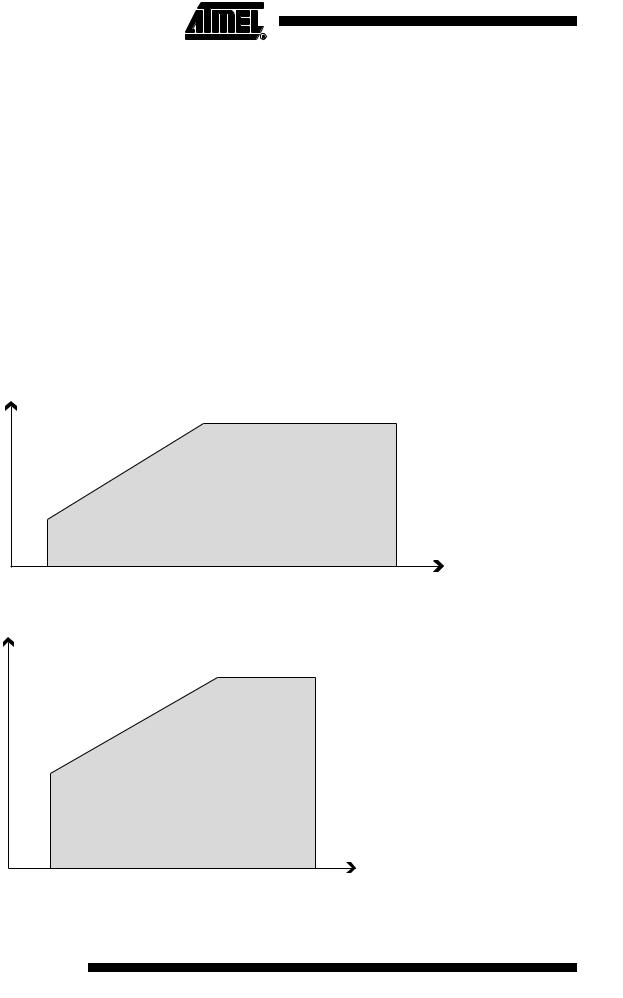

23.4Maximum Speed vs. VCC

Figure 23-2. |

Maximum Frequency vs. VCC |

|

|

|

10 MHz |

|

|

|

|

Safe Operating Area |

|

|

4 MHz |

|

|

|

1.8V |

2.7V |

5.5V |

Figure 23-3. |

Maximum Frequency vs. VCC |

|

|

|

20 MHz |

|

|

10 MHz

Safe Operating Area

2.7V |

4.5V |

5.5V |

168 ATtiny25/45/85

2586A–AVR–02/05

ATtiny25/45/85

23.5ADC Characteristics – Preliminary Data

Table 23-2. ADC Characteristics, Single Ended Channels. -40°C - 85°C

Symbol |

Parameter |

Condition |

Min(1) |

Typ(1) |

Max(1) |

Units |

|

Resolution |

Single Ended Conversion |

|

|

10 |

Bits |

|

|

|

|

|

|

|

|

|

Single Ended Conversion |

|

|

|

|

|

|

VREF = 4V, VCC = 4V, |

|

2 |

|

LSB |

|

|

ADC clock = 200 kHz |

|

|

|

|

|

|

|

|

|

|

|

|

|

Single Ended Conversion |

|

|

|

|

|

|

VREF = 4V, VCC = 4V, |

|

3 |

|

LSB |

|

Absolute accuracy (Including |

ADC clock = 1 MHz |

|

|

|

|

|

|

|

|

|

|

|

|

Single Ended Conversion |

|

|

|

|

|

|

INL, DNL, quantization error, |

|

|

|

|

|

|

VREF = 4V, VCC = 4V, |

|

|

|

|

|

|

gain and offset error) |

|

1.5 |

|

LSB |

|

|

|

ADC clock = 200 kHz |

|

|

||

|

|

|

|

|

|

|

|

|

Noise Reduction Mode |

|

|

|

|

|

|

|

|

|

|

|

|

|

Single Ended Conversion |

|

|

|

|

|

|

VREF = 4V, VCC = 4V, |

|

2.5 |

|

LSB |

|

|

ADC clock = 1 MHz |

|

|

||

|

|

|

|

|

|

|

|

|

Noise Reduction Mode |

|

|

|

|

|

|

|

|

|

|

|

|

|

Single Ended Conversion |

|

|

|

|

|

Integral Non-linearity (INL) |

VREF = 4V, VCC = 4V, |

|

1 |

|

LSB |

|

|

ADC clock = 200 kHz |

|

|

|

|

|

|

|

|

|

|

|

|

|

Single Ended Conversion |

|

|

|

|

|

Differential Non-linearity (DNL) |

VREF = 4V, VCC = 4V, |

|

0.5 |

|

LSB |

|

|

ADC clock = 200 kHz |

|

|

|

|

|

|

|

|

|

|

|

|

|

Single Ended Conversion |

|

|

|

|

|

Gain Error |

VREF = 4V, VCC = 4V, |

|

2.5 |

|

LSB |

|

|

ADC clock = 200 kHz |

|

|

|

|

|

|

|

|

|

|

|

|

|

Single Ended Conversion |

|

|

|

|

|

Offset Error |

VREF = 4V, VCC = 4V, |

|

1.5 |

|

LSB |

|

|

ADC clock = 200 kHz |

|

|

|

|

|

|

|

|

|

|

|

|

Conversion Time |

Free Running Conversion |

13 |

|

260 |

µs |

|

|

|

|

|

|

|

|

Clock Frequency |

|

50 |

|

1000 |

kHz |

|

|

|

|

|

|

|

VIN |

Input Voltage |

|

GND |

|

VREF |

V |

|

Input Bandwidth |

|

|

38.5 |

|

kHz |

|

|

|

|

|

|

|

VINT |

Internal Voltage Reference |

|

1.0 |

1.1 |

1.2 |

V |

RAIN |

Analog Input Resistance |

|

|

100 |

|

MΩ |

Note: 1. |

Values are preliminary. |

|

|

|

|

|

2.Minimum for AVCC is 1.8V.

3.Maximum for AVCC is 5.5V.

169

2586A–AVR–02/05

24. ATtiny25/45/85 Typical Characteristics – Preliminary Data - TBD

The data contained in this section is largely based on simulations and characterization of similar devices in the same process and design methods. Thus, the data should be treated as indications of how the part will behave.

The following charts show typical behavior. These figures are not tested during manufacturing. All current consumption measurements are performed with all I/O pins configured as inputs and with internal pull-ups enabled. A sine wave generator with rail-to-rail output is used as clock source.

The power consumption in Power-down mode is independent of clock selection.

The current consumption is a function of several factors such as: operating voltage, operating frequency, loading of I/O pins, switching rate of I/O pins, code executed and ambient temperature. The dominating factors are operating voltage and frequency.

The current drawn from capacitive loaded pins may be estimated (for one pin) as CL*VCC*f where

CL = load capacitance, VCC = operating voltage and f = average switching frequency of I/O pin.

The parts are characterized at frequencies higher than test limits. Parts are not guaranteed to function properly at frequencies higher than the ordering code indicates.

The difference between current consumption in Power-down mode with Watchdog Timer enabled and Power-down mode with Watchdog Timer disabled represents the differential current drawn by the Watchdog Timer.

170 ATtiny25/45/85

2586A–AVR–02/05