- •Contents

- •1. Video and Image Processing Suite Overview

- •Release Information

- •Device Family Support

- •Latency

- •In-System Performance and Resource Guidance

- •Stall Behavior and Error Recovery

- •2. Interfaces

- •Video Formats

- •Avalon-ST Video Protocol

- •Video Data Packets

- •Static Parameters of Video Data Packets

- •Control Data Packets

- •Ancillary Data Packets

- •User-Defined and Altera-Reserved Packets

- •Packet Propagation

- •Transmission of Avalon-ST Video Over Avalon-ST Interfaces

- •Packet Transfer Examples

- •Avalon-MM Slave Interfaces

- •Specification of the Type of Avalon-MM Slave Interfaces

- •Avalon-MM Master Interfaces

- •Specification of the Type of Avalon-MM Master Interfaces

- •Buffering of Non-Image Data Packets in Memory

- •3. Getting Started

- •IP Catalog and Parameter Editor

- •Specifying IP Core Parameters and Options

- •Installing and Licensing IP Cores

- •OpenCore Plus IP Evaluation

- •4. Clocked Video Interface IP Cores

- •Control Port

- •Clocked Video Input Format Detection

- •Interrupts

- •Clocked Video Output Video Modes

- •Interrupts

- •Generator Lock

- •Underflow and Overflow

- •Timing Constraints

- •Handling Ancillary Packets

- •Modules for Clocked Video Input II IP Core

- •Clocked Video Interface Parameter Settings

- •Clocked Video Interface Signals

- •Clocked Video Interface Control Registers

- •5. 2D FIR Filter IP Core

- •Calculation Precision

- •Coefficient Precision

- •Result to Output Data Type Conversion

- •2D FIR IP Core Parameter Settings

- •2D FIR Filter Signals

- •2D FIR Filter Control Registers

- •6. Video Mixing IP Cores

- •Alpha Blending

- •Video Mixing Parameter Settings

- •Video Mixing Signals

- •Video Mixing Control Registers

- •7. Chroma Resampler IP Core

- •Horizontal Resampling (4:2:2)

- •Vertical Resampling (4:2:0)

- •Chroma Resampler Parameter Settings

- •Chroma Resampler Signals

- •8. Video Clipping IP Cores

- •Video Clipping Parameter Settings

- •Video Clipping Signals

- •Video Clipping Control Registers

- •9. Color Plane Sequencer IP Core

- •Combining Color Patterns

- •Rearranging Color Patterns

- •Splitting and Duplicating

- •Subsampled Data

- •Color Plane Sequencer Parameter Settings

- •Color Plane Sequencer Signals

- •10. Color Space Conversion IP Cores

- •Input and Output Data Types

- •Color Space Conversion

- •Result of Output Data Type Conversion

- •Color Space Conversion Parameter Settings

- •Color Space Conversion Signals

- •Color Space Conversion Control Registers

- •11. Control Synchronizer IP Core

- •Using the Control Synchronizer IP Core

- •Control Synchronizer Parameter Settings

- •Control Synchronizer Signals

- •Control Synchronizer Control Registers

- •12. Deinterlacing IP Cores

- •Deinterlacing Methods

- •Bob with Scanline Duplication

- •Bob with Scanline Interpolation

- •Weave

- •Motion-Adaptive

- •Sobel-Based HQ Mode

- •Pass-Through Mode for Progressive Frames

- •Frame Buffering

- •Frame Rate Conversion

- •Bandwidth Requirement Calculations for 10-bit YCbCr Video

- •Behavior When Unexpected Fields are Received

- •Handling of Avalon-ST Video Control Packets

- •Deinterlacing Parameter Settings

- •Deinterlacing Signals

- •Deinterlacing Control Registers

- •Design Guidelines for Broadcast Deinterlacer IP Core

- •13. Frame Reader IP Core

- •Single-Cycle Color Patterns

- •Frame Reader Output Pattern and Memory Organization

- •Frame Reader Parameter Settings

- •Frame Reader Signals

- •Frame Reader Control Registers

- •14. Frame Buffer IP Cores

- •Double Buffering

- •Triple Buffering

- •Locked Frame Rate Conversion

- •Handling of Avalon-ST Video Control Packets

- •Color Format

- •Frame Buffer Parameter Settings

- •Frame Buffer Signals

- •Frame Buffer Control Registers

- •15. Gamma Corrector IP Core

- •Gamma Corrector Parameter Settings

- •Gamma Corrector Signals

- •Gamma Corrector Control Registers

- •16. Interlacer IP Core

- •Interlacer Parameter Settings

- •Interlacer Signals

- •Interlacer Control Registers

- •17. Scaler II IP Core

- •Nearest Neighbor Algorithm

- •Bilinear Algorithm

- •Bilinear Algorithmic Description

- •Polyphase and Bicubic Algorithm

- •Double-Buffering

- •Polyphase Algorithmic Description

- •Choosing and Loading Coefficients

- •Edge-Adaptive Scaling Algorithm

- •Scaler II Parameter Settings

- •Scaler II Signals

- •Scaler II Control Registers

- •18. Video Switching IP Cores

- •Mixer Layer Switching

- •Video Switching Parameter Settings

- •Video Switching Signals

- •Video Switching Control Registers

- •19. Test Pattern Generator IP Cores

- •Test Pattern

- •Generation of Avalon-ST Video Control Packets and Run-Time Control

- •Test Pattern Generator Parameter Settings

- •Test Pattern Generator Signals

- •Test Pattern Generator Control Registers

- •20. Trace System IP Core

- •Trace System Parameter Settings

- •Trace System Signals

- •Operating the Trace System from System Console

- •Loading the Project and Connecting to the Hardware

- •Trace Within System Console

- •TCL Shell Commands

- •21. Avalon-ST Video Monitor IP Core

- •Packet Visualization

- •Monitor Settings

- •Avalon-ST Video Monitor Parameter Settings

- •Avalon-ST Video Monitor Signals

- •Avalon-ST Video Monitor Control Registers

- •Avalon-ST Video Class Library

- •Running the Tests

- •Video File Reader Test

- •Example Test Environment

- •Video Field Life Cycle

- •Constrained Random Test

- •Complete Class Reference

- •c_av_st_video_control

- •c_av_st_video_data

- •c_av_st_video_file_io

- •c_av_st_video_item

- •c_av_st_video_source_sink_base

- •c_av_st_video_sink_bfm_’SINK

- •c_av_st_video_source_bfm_’SOURCE

- •c_av_st_video_user_packet

- •c_pixel

- •Raw Video Data Format

- •Cadence Detection and Reverse Pulldown in the Deinterlacer II IP Core

- •Document Revision History

- •How to Contact Altera

UG-VIPSUITE |

|

Running the Tests |

A-7 |

|

2015.01.23 |

|

|||

|

|

|

||

|

|

|

|

|

|

Class |

|

Description |

|

|

|

|

|

|

|

class c_av_st_video_file_io |

|

Parameterized class. |

|

Extends c_av_video_item. Comprises of width, height, and interlaced bits (the fields found in an Avalon-ST video control packet). It also contains data types and methods that control the addition of garbage beats that are used by other classes. The class provides methods to get and set the individual fields.

class c_av_st_user_packet |

This parameterized class is defined in a separate file (av_st_video_ |

|

file_io_class.sv) because some test environments do not use video |

|

data from a file, using constrained random data generated by the |

|

other classes instead. |

|

This class provides the following methods: |

|

• to read and write video files (in .raw format) |

|

• to send or receive videos and control packet objects to or from |

|

the mailbox. |

|

Variables that govern the file I/O details include the ability to |

|

artificially lengthen and shorten video packets and to introduce |

|

garbage beats into control packets by various get and set method |

|

calls. |

|

Typical usage of the file I/O class is to construct two objects—a |

|

reader and a writer, call the open file methods for both, call the |

|

read_file method for the reader, and repeatedly call the wait_ |

|

for_and_write_video_packet_to_file method in the writer. |

|

The parameters for this class are BITS_PER_CHANNEL and |

|

CHANNELS_PER_PIXEL. |

|

|

Running the Tests

This example system is available in the Quartus II install directory.

• For example video files test:

$(QUARTUS_ROOTDIR)/../ip/altera/vip/verification/example_video_files

• For constrained random test:

$(QUARTUS_ROOTDIR)/../ip/altera/vip/verification/ example_constrained_random

Note: The actual commands used in this section are for a Linux example. However, the same flow applies for Windows users.

1.Automatically generate the tb.v netlist from the Qsys system integration tool in the Quartus II software.

Avalon-ST Video Verification IP Suite |

Altera Corporation |

|

|

Send Feedback

A-8 |

Running the Tests |

UG-VIPSUITE |

|

2015.01.23 |

|||

|

|

a. Copy the verification files to a local directory and cd to the testbench directory.

>cp $(QUARTUS_ROOTDIR)/../ip/altera/vip/verification $ALTERA_VIDEO_VERIFICATION >cd $ALTERA_VIDEO_VERIFICATION/testbench

b.Start the Qsys system integration tool from the Quartus II software (tools > Qsys or through command line.

G:\altera\14.0\quartus\sopc_builder\bin>qsys-edit

c.Load the Qsys project. Double-click tb.qsys.

d.Update the IP search path by selecting from the Tools menu > Options > Add. Navigate to one directory higher and into the dut directory.

e.Click Open, then Finish.

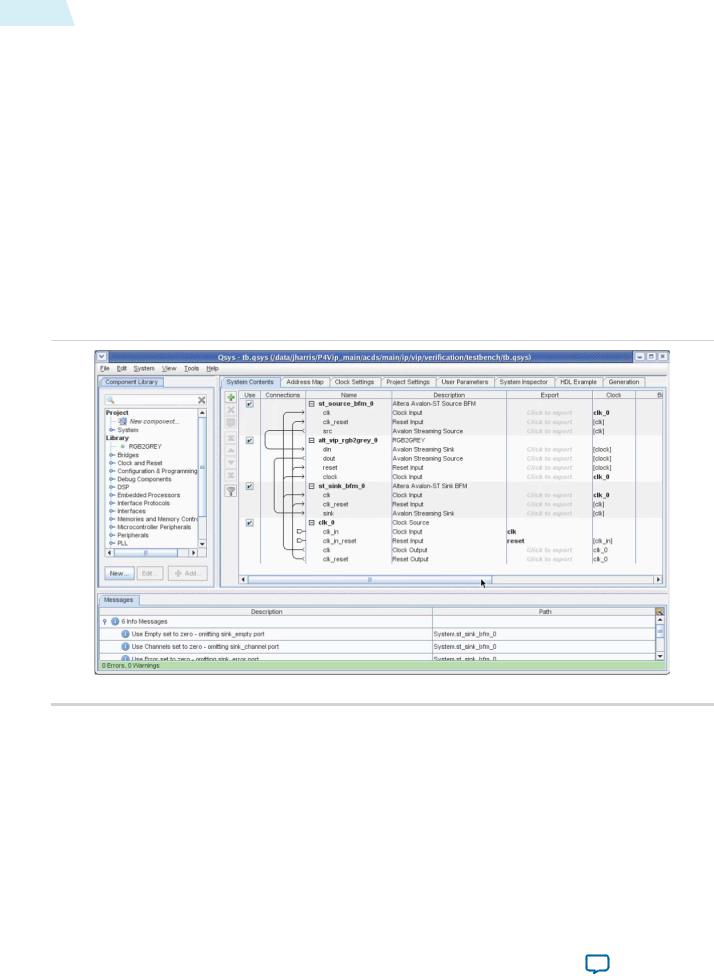

The system refreshes and shows the RGBtogreyscaleconvertor (in between Avalon-ST source and sink BFMs), which is our example DUT. You can easily replaced this example by any other user IP function.

Figure A-3: Qsys Dialog Box

f.Create the tb.v netlist from the Qsys project by selecting Generation, set Create simulation model to Verilog. Select Generate. Close the generate completed dialog box, and exit Qsys.

Qsys has now generated the tb.v netlist and all the required simulation files.

Altera Corporation |

Avalon-ST Video Verification IP Suite |

|

|

Send Feedback

UG-VIPSUITE |

Running the Tests |

A-9 |

|

2015.01.23 |

|||

|

|

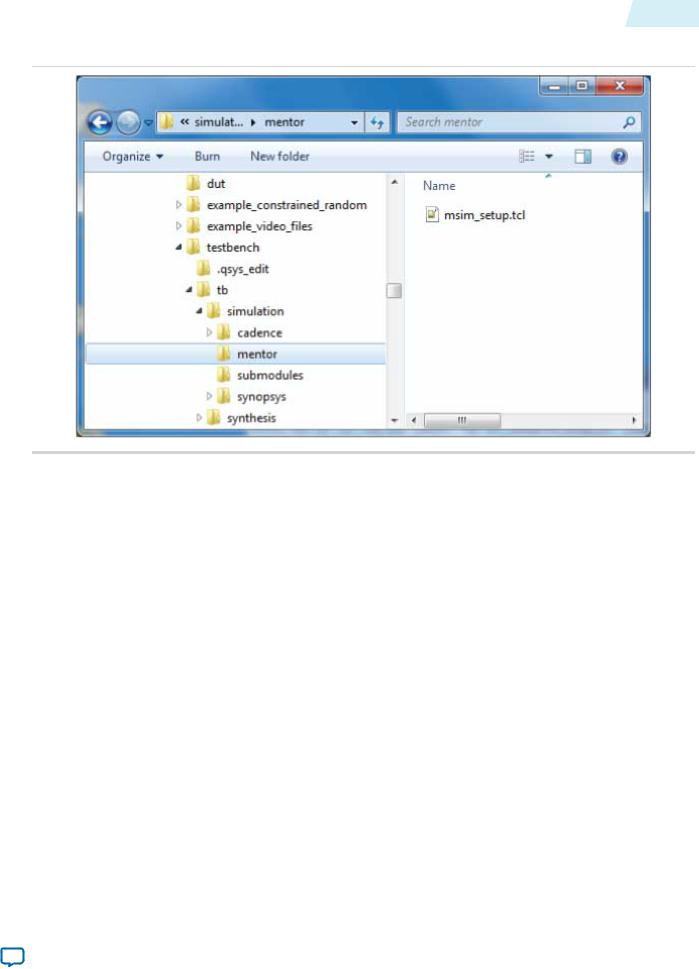

Figure A-4: tb.v Netlist

2.Run the test by changing to the example video files test or example constrained random test directory and start the QuestaSim™ software.

Note: You can also run this test with the ModelSim® software but this test does not support the ModelSim-Altera Edition (AE) or ModelSim-Altera Starter Edition (ASE) softwares.

• For example video files test:

>cd $ALTERA_VIDEO_VERIFICATION/example_video_files >vsim –do run.tcl

• For constrained random test:

>cd $ALTERA_VIDEO_VERIFICATION/example_constrained_random >vsim –do run.tcl

Note: To run with other simulators, edit the run.tcl file as provided by Qsys (including the appropriate TCL script for that vendor’s simulator). The test runs and completes with the following message:

“Simulation complete. To view resultant video, now run the windows raw2avi application.”

The example video files test produces a raw output video file (vip_car_out.raw). Together with an .spc file (vip_car_out.spc), you can use the vip_car_out.raw to generate an .avi file for viewing.

Avalon-ST Video Verification IP Suite |

Altera Corporation |

|

|

Send Feedback