- •CONTENTS

- •FIGURES

- •TABLES

- •1.1 Manual Contents

- •1.2 Notational Conventions and Terminology

- •1.3 Related Documents

- •1.4 Application Support Services

- •2.1 Typical Applications

- •2.2 Microcontroller Features

- •2.3 Functional Overview

- •2.3.1 Core

- •2.3.1.3 Register File

- •2.3.2 Memory Controller

- •2.4 Internal Timing

- •2.4.1 Clock and Power Management Logic

- •2.4.2 Internal Timing

- •2.4.2.1 Clock Failure Detection Logic

- •2.4.2.2 External Timing

- •2.4.2.3 Power Management Options

- •2.4.3 Internal Memory

- •2.4.4 Serial Debug Unit

- •2.4.5 Interrupt Service

- •2.5 Internal Peripherals

- •2.5.1 I/O Ports

- •2.5.2 Serial I/O (SIO) Port

- •2.5.3 Synchronous Serial I/O (SSIO) Port

- •2.5.4 Event Processor Array (EPA) and Timer/Counters

- •2.5.7 Stack Overflow Module

- •2.5.8 Watchdog Timer

- •2.6 Special Operating Modes

- •2.7 Chip Configuration Registers

- •3.1 Overview of the Instruction Set

- •3.1.1 BIT Operands

- •3.1.2 BYTE Operands

- •3.1.4 WORD Operands

- •3.1.5 INTEGER Operands

- •3.1.9 Converting Operands

- •3.1.10 Conditional Jumps

- •3.1.11 Floating-Point Operations

- •3.1.12 Extended Instructions

- •3.2 Addressing Modes

- •3.2.1 Direct Addressing

- •3.2.2 Immediate Addressing

- •3.2.3 Indirect Addressing

- •3.2.3.1 Extended Indirect Addressing

- •3.2.3.2 Indirect Addressing with Autoincrement

- •3.2.3.3 Extended Indirect Addressing with Autoincrement

- •3.2.3.4 Indirect Addressing with the Stack Pointer

- •3.2.4 Indexed Addressing

- •3.2.4.3 Extended Indexed Addressing

- •3.2.4.4 Zero-indexed Addressing

- •3.3 Considerations for Crossing Page Boundaries

- •3.4 Software Protection Features and Guidelines

- •4.1 Memory Map Overview

- •4.2 Memory Partitions

- •4.2.1 External Memory

- •4.2.2 Internal ROM

- •4.2.2.1 Program Memory in Page FFH

- •4.2.2.3 Reserved Memory Locations

- •4.2.2.4 Interrupt, PIH, and PTS Vectors

- •4.2.2.5 Chip Configuration Bytes

- •4.2.3 Internal RAM (Code RAM)

- •4.2.4.2 Peripheral SFRs

- •4.2.5 Register File

- •4.2.5.2 Stack Pointer (SP)

- •4.3 Windowing

- •4.3.1 Selecting a Window

- •4.3.2 Addressing a Location Through a Window

- •4.3.2.4 Unsupported Locations Windowing Example

- •4.3.2.5 Using the Linker Locator to Set Up a Window

- •4.3.3 Windowing and Addressing Modes

- •4.4 Controlling Read Access to the Internal ROM

- •4.5 Remapping Internal ROM

- •5.1 Functional Overview

- •5.2 Stack Operations

- •5.3 Stack Overflow Module Registers

- •5.4 Programming the Stack Overflow Module

- •5.4.1 Initializing the Stack Pointer

- •5.4.2 Enabling the Stack Overflow Module and Specifying Stack Boundaries

- •6.1 Overview of the Interrupt Control Circuitry

- •6.2 Interrupt Signals and Registers

- •6.3 Interrupt Sources, Priorities, and Vector Addresses

- •6.3.1 PIH Interrupt Sources, Priorities, and Vector Addresses

- •6.3.1.1 Using Software to Provide the Vector Address

- •6.3.1.2 Providing the Vector Address in Response to a CPU Request

- •6.3.2 Special Interrupts

- •6.3.2.1 Unimplemented Opcode

- •6.3.2.2 Software Trap

- •6.3.2.4 Stack Overflow

- •6.3.3 External Interrupt Signal

- •6.3.4 Shared Interrupt Requests

- •6.4 Interrupt Latency

- •6.4.1 Situations that Increase Interrupt Latency

- •6.4.2 Calculating Latency

- •6.4.2.2 PTS Interrupt Latency

- •6.5 Programming the Interrupts

- •6.5.1 Modifying Interrupt Priorities

- •6.5.2 Determining the Source of an Interrupt

- •6.6 Initializing the PTS Control Blocks

- •6.6.1 Specifying the PTS Count

- •6.6.2 Selecting the PTS Mode

- •6.6.3 Single Transfer Mode

- •6.6.4 Block Transfer Mode

- •6.6.5 Dummy Mode

- •7.1 I/O Ports Overview

- •7.2 Configuring the Port Pins

- •7.2.2 Configuring Ports 3 and 4 (Address/Data Bus)

- •7.2.3 Port Configuration Example

- •7.3.1 Address and Data Signals (Ports 3, 4, and EPORT)

- •7.3.1.1 EPORT Status During Reset, CCB Fetch, Idle, Powerdown, and Hold

- •7.3.5 External Interrupt Signal (Port 2)

- •7.3.6 PWM Signals (Port 11)

- •7.3.7 Serial I/O Port Signals (Ports 2 and 7)

- •7.3.8 Special Operating Mode Signal (Port 5 Pin 7)

- •7.3.9 Synchronous Serial I/O Port Signals (Port 10)

- •7.4 I/O Port Internal Structures

- •7.4.3 Internal Structure for Ports 3 and 4 (Address/Data Bus)

- •8.1 Serial I/O (SIO) Port Functional Overview

- •8.2 Serial I/O Port Signals and Registers

- •8.3 Serial Port Modes

- •8.3.1 Synchronous Mode (Mode 0)

- •8.3.2 Asynchronous Modes (Modes 1, 2, and 3)

- •8.3.2.1 Mode 1

- •8.3.2.2 Mode 2

- •8.3.2.3 Mode 3

- •8.3.2.4 Multiprocessor Communications

- •8.4 Programming the Serial Port

- •8.4.1 Configuring the Serial Port Pins

- •8.4.2 Programming the Control Register

- •8.4.3 Programming the Baud Rate and Clock Source

- •8.4.4 Enabling the Serial Port Interrupts

- •8.4.5 Determining Serial Port Status

- •CHAPTER 9 Synchronous Serial I/O (SSIO) Port

- •9.1 SSIO Port Overview

- •9.1.1 Standard Mode

- •9.1.2 Duplex Mode

- •9.2 SSIO pORT sIGNALS AND rEGISTERS

- •9.3 ssio Port Operation

- •9.3.1 Transmitting and Receiving Data

- •9.3.1.1 Normal Transfers (All Modes)

- •9.3.1.2 Handshaking Transfers (Standard Mode Only)

- •9.4 Programming the SSIO Port

- •9.4.1 Configuring the SSIO Port Pins

- •9.4.2 Configuring the SSIO Registers

- •9.4.2.1 The SSIO Baud (SSIO_BAUD) Register

- •9.4.2.3 The SSIO 0 Clock (SSIO0_CLK) Register

- •9.4.2.4 The SSIO 1 Clock (SSIO1_CLK) Register

- •9.4.3 Enabling the SSIO Interrupts

- •9.5 Programming Considerations

- •9.5.2 Standard Mode Considerations

- •9.5.3 Duplex Mode Considerations

- •10.1 PWM FUNCTIONAL OVERVIEW

- •10.2 PWM Signals and Registers

- •10.3 pwm operation

- •10.4 Programming the Frequency and Period

- •10.5 Programming the Duty Cycle

- •10.5.1 Sample Calculations

- •10.5.2 Reading the Current Value of the Down-counter

- •10.5.3 Enabling the PWM Outputs

- •10.5.4 Generating Analog Outputs

- •11.1 EPA Functional Overview

- •11.2 EPA and Timer/Counter Signals and Registers

- •11.3 Timer/Counter Functional Overview

- •11.3.1 Timer Multiplexing on the Time Bus

- •11.4 EPA Channel Functional Overview

- •11.4.1 Operating in Input Capture Mode

- •11.4.2 Operating in Output Compare Mode

- •11.4.3 Operating in Compare Mode with the Output/Simulcapture Channels

- •11.4.4 Generating a 32-bit Time Value

- •11.4.5 Controlling a Pair of Adjacent Pins

- •11.5 Programming the EPA and Timer/Counters

- •11.5.1 Configuring the EPA and Timer/Counter Signals

- •11.5.2 Programming the Timers

- •11.5.3 Programming the Capture/Compare Channels

- •11.5.4 Programming the Compare-only (Output/Simulcapture) Channels

- •11.6 Enabling the EPA Interrupts

- •11.7 Determining Event Status

- •CHAPTER 12 Analog-to-digital (A/D) Converter

- •12.1 A/D Converter Functional Overview

- •12.2 A/D Converter Signals and Registers

- •12.3 A/D Converter Operation

- •12.4 Programming the A/D Converter

- •12.4.1 Programming the A/D Test Register

- •12.4.2 Programming the A/D Result Register (for Threshold Detection Only)

- •12.4.3 Programming the A/D Time Register

- •12.4.4 Programming the A/D Command Register

- •12.4.5 Programming the A/D Scan Register

- •12.4.6 Enabling the A/D Interrupt

- •12.5 Determining A/D Status and Conversion Results

- •12.6 Design Considerations

- •12.6.1 Designing External Interface Circuitry

- •12.6.1.1 Minimizing the Effect of High Input Source Resistance

- •12.6.1.2 Suggested A/D Input Circuit

- •12.6.1.3 Analog Ground and Reference Voltages

- •12.6.2 Understanding A/D Conversion Errors

- •CHAPTER 13 Minimum Hardware Considerations

- •13.1 Minimum Connections

- •13.1.1 Unused Inputs

- •13.1.2 I/O Port Pin Connections

- •13.2 Applying and Removing Power

- •13.3 Noise Protection Tips

- •13.4 The On-chip Oscillator Circuitry

- •13.5 Using an External Clock Source

- •13.6 Resetting the Microcontroller

- •13.6.1 Generating an External Reset

- •13.6.2 Issuing the Reset (RST) Instruction

- •13.6.3 Issuing an Illegal IDLPD Key Operand

- •13.6.4 Enabling the Watchdog Timer

- •13.6.5 Detecting Clock Failure

- •13.7 Identifying the Reset Source

- •14.1 Special Operating Mode Signals and Registers

- •14.2 Reducing Power Consumption

- •14.3 Idle Mode

- •14.3.1 Enabling and Disabling Idle Mode

- •14.3.2 Entering and Exiting Idle Mode

- •14.4 Powerdown Mode

- •14.4.1 Enabling and Disabling Powerdown Mode

- •14.4.2 Entering Powerdown Mode

- •14.4.3 Exiting Powerdown Mode

- •14.4.3.1 Generating a Hardware Reset

- •14.4.3.2 Asserting the External Interrupt Signal

- •14.4.3.3 Selecting an External Capacitor

- •14.5 ONCE Mode

- •CHAPTER 15 Interfacing with External Memory

- •15.1 Internal and External Addresses

- •15.2 External Memory Interface Signals and Registers

- •15.3 The Chip-select Unit

- •15.3.1 Defining Chip-select Address Ranges

- •15.3.2 Controlling Bus Parameters

- •15.3.3 Chip-select Unit Initial Conditions

- •15.3.4 Programming the Chip-select Registers

- •15.3.5 Example of a Chip-select Setup

- •15.4 Chip Configuration Registers and Chip Configuration Bytes

- •15.5 Bus Width and Multiplexing

- •15.5.1 A 16-bit Example System

- •15.5.2 16-bit Bus Timings

- •15.5.3 8-bit Bus Timings

- •15.5.4 Comparison of Multiplexed and Demultiplexed Buses

- •15.6 Wait States (Ready Control)

- •15.7 Bus-hold Protocol

- •15.7.1 Enabling the Bus-hold Protocol

- •15.7.2 Disabling the Bus-hold Protocol

- •15.7.3 Hold Latency

- •15.7.4 Regaining Bus Control

- •15.8 Write-control Modes

- •15.9 System Bus AC Timing Specifications

- •15.9.1 Deferred Bus-cycle Mode

- •15.9.2 Explanation of AC Symbols

- •15.9.3 AC Timing Definitions

- •16.1 Serial Debug Unit (SDU) Functional Overview

- •16.2 SDU Signals and Registers

- •16.3 SDU Operation

- •16.3.1 SDU State Machine

- •16.3.2 Code RAM Access State Machine

- •16.3.3 Minimizing Latency

- •16.4 Code RAM Access

- •16.4.1 Code RAM Data Transfer

- •16.4.2 Code RAM Access Instructions

- •16.4.3 Code RAM Data Transfer Example

- •16.5 SDU Interface Connector

- •17.1 Signals and Registers

- •17.2 Memory Protection Options

- •17.3 Entering Test-ROM Routines

- •17.3.1 Power-up and Power-down Sequences

- •17.4 ROM-dump Routine and Circuit

- •17.5 Serial Port Mode Routine

- •17.5.1 Serial Port RISM

- •17.5.2 Serial Port Mode Circuit

- •17.6 SDU RISM Execution Routine

- •17.6.1 SDU RISM Data Transfer

- •17.6.1.1 SDU RISM Data Transfer Before

- •17.6.1.2 SDU RISM Data Transfer After

- •17.6.2 SDU RISM Execution Circuit

- •17.7 RISM Command Descriptions

- •17.8 Executing Programs from Register RAM

- •17.9 RISM Command Examples

- •17.9.1 Serial Port Mode RISM Read Command Example

- •17.9.2 Serial Port Mode RISM Write Command Example

- •17.9.3 SDU RISM Execution Write Command Example

- •17.9.4 SDU RISM Execution Go Command Example

- •B.1 Functional Groupings of Signals

- •B.2 Signal Descriptions

- •B.3 Default Conditions

8XC196EA USER’S MANUAL

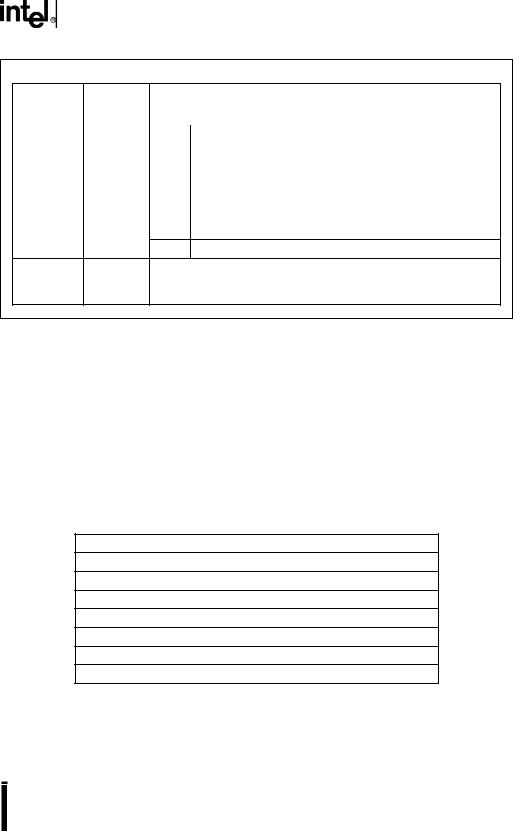

Table 6-8. Single Transfer Mode PTSCB

Unused

Unused

PTSDST (H) = 60H

PTSDST (L) = 00H

PTSSRC (H) = 00H

PTSSRC (L) = 20H

PTSCON = A5H (Mode = 101, BW = 0, SI/SU = 0, DI/DU = 1)

PTSCOUNT = 09H

6.6.4Block Transfer Mode

In block transfer mode, an interrupt causes the PTS to move a block of bytes or words from one memory location to another. See AP-445, 8XC196KR Peripherals: A User’s Point of View , for application examples with code. Figure 6-25 shows the PTS control block for block transfer mode.

In this mode, each PTS cycle consists of the transfer of an entire block of bytes or words. Because a PTS cycle cannot be interrupted, the block transfer mode can create long interrupt latency. The worst-case latency could be as high as 500 states if you assume a block transfer of 32 words from one external memory location to another, using an 8-bit bus with no wait states. See Table 6-6 on page 6-18 for execution times of PTS cycles.

The PTSCB in Table 6-9 sets up three PTS cycles that will transfer five bytes from memory locations 20–24H to 6000–6004H (cycle 1), 6005–6009H (cycle 2), and 600A–600EH (cycle 3). The source and destination are incremented after each byte transfer, but the original source address is reloaded into PTSSRC at the end of each block-transfer cycle. In this routine, the PTS always gets the first byte from location 20H.

Table 6-9. Block Transfer Mode PTSCB

Unused

PTSBLOCK = 05H

PTSDST (H) = 60H

PTSDST (L) = 00H

PTSSRC (H) = 00H

PTSSRC (L) = 20H

PTSCON = 37H (Mode = 001; DI, SI, DU, BW = 1; SU = 0)

PTSCOUNT = 03H

6-38

STANDARD AND PTS INTERRUPTS

PTS Block Transfer Mode Control Block

In block transfer mode, the PTS control block contains a block size (PTSBLOCK), a source and destination address (PTSSRC and PTSDST), a control register (PTSCON), and a transfer count (PTSCOUNT).

|

|

7 |

|

|

|

|

|

|

|

|

|

0 |

|

|

|

Unused |

|

0 |

0 |

0 |

|

0 |

|

0 |

0 |

|

0 |

0 |

|

|

|

|

7 |

|

|

|

|

|

|

|

|

|

0 |

|

|

PTSBLOCK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PTS Block Size |

|

|

|

|

|

|||

|

|

|

15 |

|

|

|

|

|

|

|

|

|

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PTSDST (H) |

|

|

|

PTS Destination Address (high byte) |

|

|

|

||||||

|

|

|

7 |

|

|

|

|

|

|

|

|

|

0 |

|

|

PTSDST (L) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PTS Destination Address (low byte) |

|

|

|

|||||||

|

|

|

15 |

|

|

|

|

|

|

|

|

|

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PTSSRC (H) |

|

|

|

|

PTS Source Address (high byte) |

|

|

|

|||||

|

|

|

7 |

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PTSSRC (L) |

|

|

|

|

PTS Source Address (low byte) |

|

|

|

|||||

|

|

|

7 |

|

|

|

|

|

|

|

|

|

0 |

|

|

PTSCON |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

M2 |

M1 |

M0 |

|

BW |

|

SU |

DU |

|

SI |

DI |

|

|

|

|

|

7 |

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PTSCOUNT |

|

|

|

|

Consecutive Block Transfers |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Register |

Location |

|

|

|

|

|

Function |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

PTSBLOCK |

PTSCB + 6 |

PTS Block Size |

|

|

|

|

|

|

|

||||

|

|

|

|

Specifies the number of bytes or words in each block. Valid values are |

|

|||||||||

|

|

|

|

1–32, inclusive. |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

||||

|

PTSDST |

PTSCB + 4 |

PTS Destination Address |

|

|

|

|

|

|

|

||||

|

|

|

|

Write the destination memory location to this register. A valid address is |

|

|||||||||

|

|

|

|

any unreserved memory location within page 00H; however, it must |

|

|||||||||

|

|

|

|

point to an even address if word transfers are selected. |

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

||||

|

PTSSRC |

PTSCB + 2 |

PTS Source Address |

|

|

|

|

|

|

|

||||

|

|

|

|

Write the source memory location to this register. A valid address is any |

|

|||||||||

|

|

|

|

unreserved memory location within page 00H; however, it must point to |

|

|||||||||

|

|

|

|

an even address if word transfers are selected. |

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Figure 6-25. PTS Control Block — Block Transfer Mode

6-39

8XC196EA USER’S MANUAL

PTS Block Transfer Mode Control Block (Continued)

|

Register |

Location |

|

|

|

|

|

Function |

|

|

|

|

|

|

|

|

|||

|

PTSCON |

PTSCB + 1 |

PTS Control Bits |

|

|

|

|||

|

|

|

|

|

|

|

|

||

|

|

|

M2:0 |

PTS Mode |

|

|

|

||

|

|

|

|

These bits select the PTS mode: |

|

||||

|

|

|

|

M2 |

M1 |

M0 |

|

|

|

|

|

|

|

0 |

|

0 |

1 |

block transfer mode |

|

|

|

|

|

|

|

|

|||

|

|

|

BW |

Byte/Word Transfer |

|

|

|||

|

|

|

|

0 |

= word transfer |

|

|

||

|

|

|

|

1 |

= byte transfer |

|

|

||

|

|

|

|

|

|

|

|||

|

|

|

SU |

Update PTSSRC |

|

|

|||

|

|

|

|

0 |

= |

reload original PTS source address after each block |

|

||

|

|

|

|

|

|

transfer is complete |

|

||

|

|

|

|

1 |

= |

retain current PTS source address after each block transfer |

|

||

|

|

|

|

|

|

is complete |

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

DU |

Update PTSDST |

|

|

|||

|

|

|

|

0 |

= |

reload original PTS destination address after each block |

|

||

|

|

|

|

|

|

transfer is complete |

|

||

|

|

|

|

1 |

= |

retain current PTS destination address after each block |

|

||

|

|

|

|

|

|

transfer is complete |

|

||

|

|

|

|

|

|

||||

|

|

|

SI |

PTSSRC Autoincrement |

|

||||

|

|

|

|

0 |

= |

the contents of PTSSRC are not incremented after each |

|

||

|

|

|

|

|

|

byte or word transfer |

|

||

|

|

|

|

1 |

= |

the contents of PTSSRC are incremented after each byte |

|

||

|

|

|

|

|

|

or word transfer |

|

|

|

|

|

|

|

|

|

||||

|

|

|

DI |

PTSDST Autoincrement |

|

||||

|

|

|

|

0 |

= |

the contents of PTSDST are not incremented after each |

|

||

|

|

|

|

|

|

byte or word transfer |

|

||

|

|

|

|

1 |

= |

the contents of PTSDST are incremented after each byte or |

|

||

|

|

|

|

|

|

word transfer |

|

|

|

|

|

|

|

|

|

|

|||

|

PTSCOUNT |

PTSCB + 0 |

Consecutive Block Transfers |

|

|

||||

|

|

|

Defines the number of blocks that will be transferred during the block |

|

|||||

|

|

|

transfer routine. Each block transfer is one PTS cycle. Maximum number |

|

|||||

|

|

|

is 255. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Figure 6-25. PTS Control Block — Block Transfer Mode (Continued)

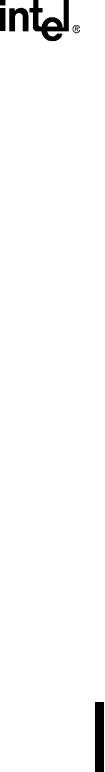

6.6.5Dummy Mode

The PTS dummy mode protects against situations where software manually clears the pending bits in the PIHx_PEND register before clearing the PIHx_PTS interrupt pending bit in the INT_PEND1 register. In this situation, the CPU may attempt to service the interrupt request after it is no longer valid. If this occurs, the PIH responds with the dummy PTS request vector address (2016H). The PTS aborts service when it reads the PTSCB and determines that the PTS dummy mode is selected. Write 0000H to location FF2016H so that the dummy PTS routine vectors to the zero-register and no register RAM locations are wasted. Figure 6-26 shows the PTS control block for dummy mode.

6-40

STANDARD AND PTS INTERRUPTS

PTS Dummy Mode Control Block

In dummy mode, the PTS control block contains only a control register (PTSCON). All other PTSCB bytes can be used as extra RAM.

|

7 |

|

|

|

|

|

|

|

|

|

|

0 |

|

PTSCON |

|

M2 |

M1 |

M0 |

|

|

0 |

|

0 |

|

0 |

0 |

0 |

|

|

7 |

|

|

|

|

|

|

|

|

|

|

0 |

Unused |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

|

|

0 |

|

0 |

|

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Register |

Location |

|

|

|

|

|

|

Function |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

||

Register |

Location |

|

|

|

|

|

|

Function |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

||||

PTSCON |

PTSCB + 1 |

PTS Control Bits |

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

M2:0 |

PTS Mode |

|

|

|

|

|

|

|

||

|

|

|

|

These bits select the PTS mode: |

|

|

|

||||||

|

|

|

|

M2 |

M1 |

M0 |

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

|

0 |

dummy mode |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Figure 6-26. PTS Control Block — Dummy Mode

6.6.6Missed-Event Mode

In missed-event mode, the PTS uses a pair of event processor array (EPA) capture/compare channels to generate an interrupt if an input pulse fails to occur within a predictable period of time (Figure 6-27). The PTS monitors a series of regular input pulses on the EPA channel and calculates when the next pulse should occur based upon the time of the last two pulses. It stores the calculated value into the event-time register (EPAx_TIME) of a second EPA channel. The second EPA channel compares the timer value to the contents of EPAx_TIME. If the next pulse does not occur before the two values are equal, an interrupt occurs. Figure 6-28 shows the PTS control block for missed-event mode.

Missing Pulse(s) |

A4295-01 |

Figure 6-27. An Example of a Missed Event

6-41

8XC196EA USER’S MANUAL

PTS Missed-event Mode Control Block

In missed-event mode, the PTS control block contains a pointer to the current event-time (PTSCUR), a pointer to the previous event-time (PTSPREV), a control register (PTSCON), and a maximum count register (PTSCOUNT).

|

|

7 |

|

|

|

|

|

|

|

|

|

0 |

|

Unused |

|

0 |

0 |

0 |

0 |

|

|

0 |

0 |

|

0 |

0 |

|

|

|

|

7 |

|

|

|

|

|

|

|

|

|

0 |

Unused |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

|

|

0 |

0 |

|

0 |

0 |

||

|

|

|

15 |

|

|

|

|

|

|

|

|

|

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PTSPREV (H) |

|

|

|

Pointer to Previous Event Time (high byte) |

|

|

|||||||

|

|

|

7 |

|

|

|

|

|

|

|

|

|

0 |

PTSPREV (L) |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

Pointer to Previous Event Time (low byte) |

|

|

||||||||

|

|

|

15 |

|

|

|

|

|

|

|

|

|

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PTSCUR (H) |

|

|

|

Pointer to Current Event Time (high byte) |

|

|

|||||||

|

|

|

7 |

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PTSCUR (L) |

|

|

|

Pointer to Current Event Time (low byte) |

|

|

|||||||

|

|

|

7 |

|

|

|

|

|

|

|

|

|

0 |

PTSCON |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

M2 |

M1 |

M0 |

BW |

|

|

0 |

0 |

|

0 |

0 |

||

|

|

|

7 |

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PTSCOUNT |

|

|

|

|

Maximum Count |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Register |

|

Location |

|

|

|

|

|

Function |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

PTSPREV |

|

PTSCB + 4 |

Pointer to Previous Event Time |

|

|

|

|

|

|||||

|

|

|

|

This register points to the memory location where the PTS stores the |

|||||||||

|

|

|

|

time of the previous event. A valid address is any unreserved memory |

|||||||||

|

|

|

|

location within page 00H; however, it must point to an even address if |

|||||||||

|

|

|

|

word event times are selected. |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|||||

PTSCUR |

|

PTSCB + 2 |

Pointer to Current Event Time |

|

|

|

|

|

|||||

|

|

|

|

This register points to the event-time register (EPAx_TIME) for the EPA |

|||||||||

|

|

|

|

channel that is capturing the input pulse signal. |

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Figure 6-28. PTS Control Block — Missed-event Mode

6-42

STANDARD AND PTS INTERRUPTS

PTS Missed-event Mode Control Block (Continued)

Register |

Location |

|

|

|

Function |

|

|

|

|

|

|

||

PTSCON |

PTSCB + 1 PTS Control Bits |

|

|

|||

|

|

|

|

|

|

|

|

|

M2:0 |

PTS Mode |

|

|

|

|

|

|

These bits select the PTS mode: |

|||

|

|

|

M2 |

M1 |

M0 |

|

|

|

|

1 |

1 |

0 |

missed-event mode |

|

|

|

|

|||

|

|

BW |

Byte/Word Event-time Value |

|||

0 = word

1 = byte

4:0 To guarantee proper device operation, write zeros to these bits.

PTSCOUNT PTSCB + 0 Maximum Count

Defines the number of times the PTS will check for the occurrence of an event. Each comparison is one PTS cycle. Maximum number is 255.

Figure 6-28. PTS Control Block — Missed-event Mode (Continued)

To use the missed-event mode, configure one event processor array (EPA) channel to capture events and a second EPA channel to monitor a timer/counter and compare its value with the expected next event time. For example, configure EPA1 as the input capture channel and EPA0 as the compare-only channel.

Configure EPA1 to select timer 1, capture on rising edge, select associated pin for input, reset timer 1, old data lost on overrun, no module concantenation (EPA1_CON = 0000 0010 X0X0 0010).

Configure EPA0 to select timer 1, compare mode, interrupt only, no action (EPA0_CON = 0000 0100 0000 0000).

Initialize the PTSCB as shown in Table 6-10.

Table 6-10. Missed-event Mode PTSCBs

0000H (Unused)

0000H (Unused)

PTSPREV (H) = xxH (any unreserved memory location within page 00H)

PTSPREV (L) = xxH (any unreserved memory location within page 00H)

PTSCUR (H) = 1FH (EPA1_TIME)

PTSCUR (L) = 5AH (EPA1_TIME)

PTSCON = C0H (missed-event mode)

PTSCOUNT = FFH (check for 255 events)

Whenever an event occurs on EPA1, the EPA loads the value of the reference timer into the EPA1_TIME register. The PTS uses two temporary registers to calculate the expected next event time. The following steps outline a missed-event PTS cycle.

6-43

8XC196EA USER’S MANUAL

1.EPA1 captures an event and the value of the reference timer is loaded into EPA1_TIME.

2.The PTS subtracts the time of the previous event, which is stored in a memory location pointed to by the PTSPREV register, from the current event-time stored in EPA1_TIME. It then loads the result into a temporary register.

TEMP1 ← (EPA1_TIME) – (PTSPREV)

For example, assume that the previous event occurred at timer value 04H and the current event occurred at timer value 08H. The PTS would load 04H into TEMP1.

3.To calculate the expected next event time, the PTS divides the contents of the temporary register (TEMP1) by two and loads the result into a second temporary register (TEMP2). It then adds the contents of TEMP1 to the contents of TEMP2 and loads the result into TEMP1. Then the PTS adds TEMP1 to the current event-time value to calculate the next event time. It stores this value in TEMP1.

TEMP2 ← TEMP1/2 TEMP1 ← TEMP1 + TEMP2

TEMP1 ← TEMP1 + EPA1_TIME

In the case of our example, TEMP1 would now contain 0EH.

4.The PTS loads the expected next event time into the location pointed to by EPA1_TIME + 4, which in this example, is the address of the EPA0_TIME register.

(EPA0_TIME) ← TEMP1

5.The PTS then loads the current event-time value into the location pointed to by the PTSPREV register.

(PTSPREV) ← (EPA1_TIME)

6.Finally, the PTS decrements the PTSCOUNT register.

PTSCOUNT ← PTSCOUNT – 1

If a match occurs between the reference timer and the contents of EPA0_TIME, EPA0 causes an interrupt which indicates a missed-event. As long as an event occurs on EPA1 before a match occurs between the reference timer and the contents of EPA0_TIME, the PTS cycle repeats until PTSCOUNT decrements to zero. When PTSCOUNT reaches zero, the PTS generates an end-of- PTS interrupt.

6-44

7

I/O Ports